Your Memory architecture in vlsi design images are ready in this website. Memory architecture in vlsi design are a topic that is being searched for and liked by netizens now. You can Get the Memory architecture in vlsi design files here. Get all free photos.

If you’re looking for memory architecture in vlsi design images information connected with to the memory architecture in vlsi design topic, you have come to the right site. Our site frequently provides you with suggestions for viewing the maximum quality video and image content, please kindly search and locate more enlightening video articles and images that fit your interests.

Memory Architecture In Vlsi Design. The goal of the project is to develop a sort algorithm to run on an mMPU which is based on emerging memory technology of ReRAM. Sketch our vision of a VLSI architecture in 2009 in Section 4. Architecture of 3D DVLSI System Interconnect Wide SIMD Vector CORE GPP CORE System Many-Banked LM Cache Global Memory Wide SIMD Vector CORE GPPLevel SVP CORE Many-Banked LM CacheCORE g MD. Cell array design with row-driven source line in block shunt architecture applicable to future 6f 2 1t1mtj memory.

3d Flash Memory Management Vlsi From vlsi.eelabs.technion.ac.il

3d Flash Memory Management Vlsi From vlsi.eelabs.technion.ac.il

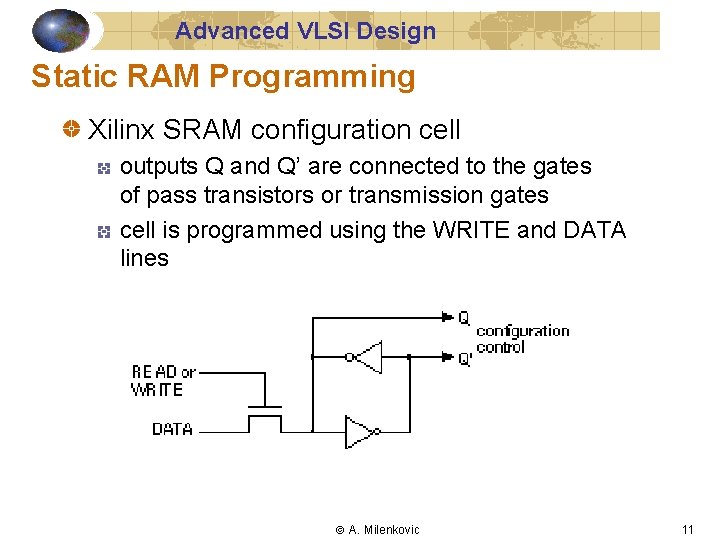

Other clocking and access logic factored out into periphery. A 0 A_b 1 bit 1 bit_b 0 Force A_b low then A. 7 SRAM Write Drive one bitline high the other low Then turn on wordline Bitlines overpower cell with new value Ex. Advanced topics in system-level design issues z Description language issues C-based system description z z. The fundamental chal-lenges involved in building such a system. This is obtained by repetitive arrangement of rectangular macro blocks which can be interconnected using wiring by abutment.

Architecture of 3D DVLSI System Interconnect Wide SIMD Vector CORE GPP CORE System Many-Banked LM Cache Global Memory Wide SIMD Vector CORE GPPLevel SVP CORE Many-Banked LM CacheCORE g MD.

The fundamental chal-lenges involved in building such a system. Intels 22nm SRAM cell. Sketch our vision of a VLSI architecture in 2009 in Section 4. The fundamental chal-lenges involved in building such a system. Other clocking and access logic factored out into periphery. Provide address to access a word of data No correlation between successive addresses Block oriented.

Source: slidetodoc.com

Source: slidetodoc.com

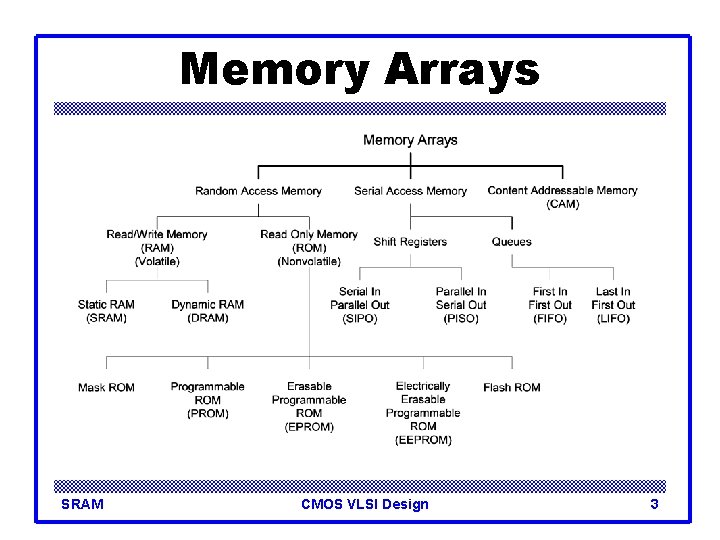

The storage array made up of cells circuits which is shared a connection in horizontal rows and vertical column. Synthesized using the memory efficient architecture. SRAM CMOS VLSI Design 4th Ed. 14 Decoders n2 ndecoder consists of 2 n-input AND gates One needed for each row of memory Build AND from NAND or NOR gates Static CMOS Pseudo-nMOS. In 2019 International Symposium on VLSI Technology Systems and Application VLSI-TSA 2019 8804671 2019 International Symposium on VLSI Technology Systems and Application VLSI.

Source: pinterest.com

Source: pinterest.com

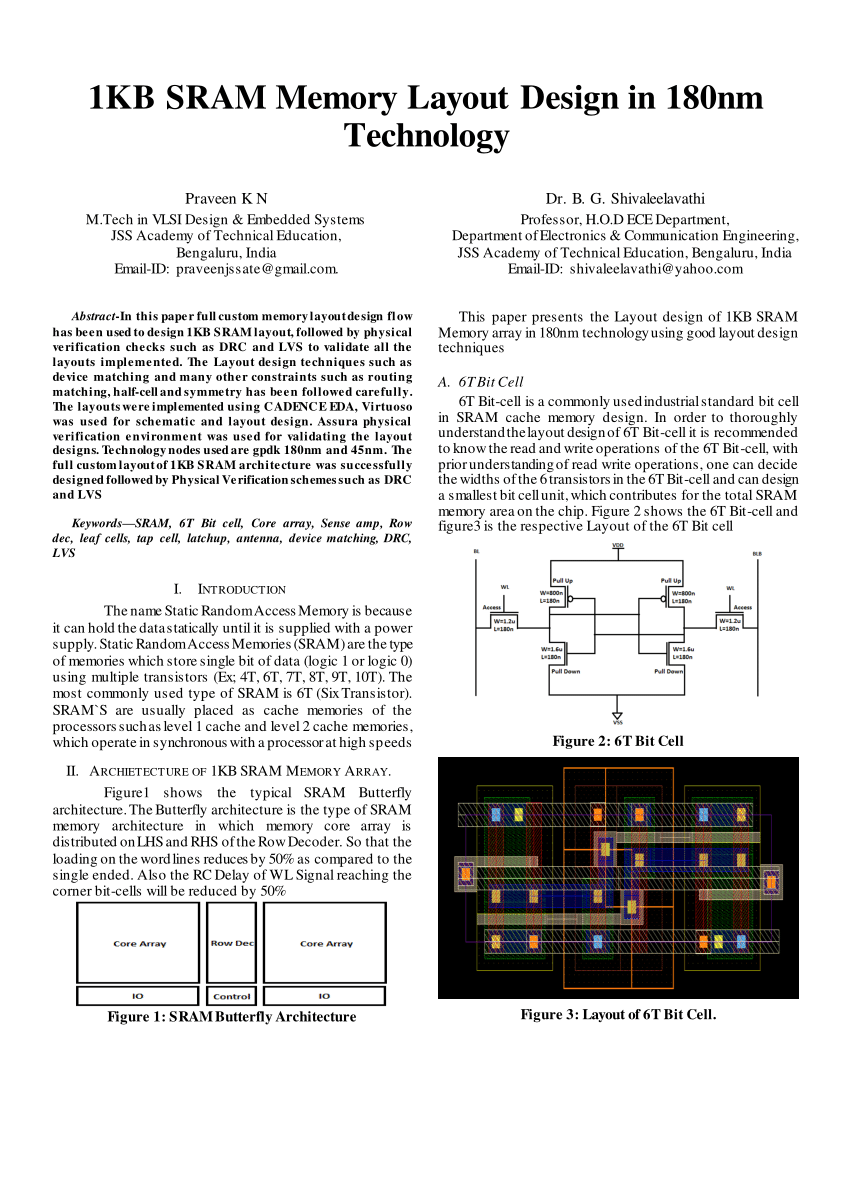

Architecture of 3D DVLSI System Interconnect Wide SIMD Vector CORE GPP CORE System Many-Banked LM Cache Global Memory Wide SIMD Vector CORE GPPLevel SVP CORE Many-Banked LM CacheCORE g MD. In terms of memory access hardware regularity and simplicity and throughput the proposed VLSI architecture is more efficient than the previously proposedKeywords. In 2019 International Symposium on VLSI Technology Systems and Application VLSI-TSA 2019 8804671 2019 International Symposium on VLSI Technology Systems and Application VLSI. SRAM Memory Layout Design in 180nm Technology Praveen K N MTech in VLSI Design Embedded Systems JSS Academy of Technical Education Bengaluru India B. The fundamental chal-lenges involved in building such a system.

Source: slidetodoc.com

Source: slidetodoc.com

A 0 A_b 1 bit 1 bit_b 0 Force A_b low then A. A 0 A_b 1 bit 1 bit_b 0 Force A_b low then A. In terms of memory access hardware regularity and simplicity and throughput the proposed VLSI architecture is more efficient than the previously proposedKeywords. Structured VLSI design is a modular methodology originated by Carver Mead and Lynn Conway for saving microchip area by minimizing the interconnect fabrics area. This is obtained by repetitive arrangement of rectangular macro blocks which can be interconnected using wiring by abutment.

Source: slidetodoc.com

Source: slidetodoc.com

This is obtained by repetitive arrangement of rectangular macro blocks which can be interconnected using wiring by abutment. In terms of memory access hardware regularity and simplicity and throughput the proposed VLSI architecture is more efficient than the previously proposedKeywords. 7 SRAM Write Drive one bitline high the other low Then turn on wordline Bitlines overpower cell with new value Ex. Synthesized using the memory efficient architecture. Large on-chip memories built from arrays of static RAM bitcells where each bit cell holds a bistable cross- coupled inverters and two access transistors.

Source: researchgate.net

Source: researchgate.net

In terms of memory access hardware regularity and simplicity and throughput the proposed VLSI architecture is more efficient than the previously proposedKeywords. Large on-chip memories built from arrays of static RAM bitcells where each bit cell holds a bistable cross- coupled inverters and two access transistors. SRAM Memory Layout Design in 180nm Technology Praveen K N MTech in VLSI Design Embedded Systems JSS Academy of Technical Education Bengaluru India B. In 2019 International Symposium on VLSI Technology Systems and Application VLSI-TSA 2019 8804671 2019 International Symposium on VLSI Technology Systems and Application VLSI. Provide address to access a word of data No correlation between successive addresses Block oriented.

Source: pinterest.com

Source: pinterest.com

A 0 A_b 1 bit 1 bit_b 0 Force A_b low then A. The system is built from 4Gb DRAM chips each of which contains 64 small but powerful processors. Architecture of 3D DVLSI System Interconnect Wide SIMD Vector CORE GPP CORE System Many-Banked LM Cache Global Memory Wide SIMD Vector CORE GPPLevel SVP CORE Many-Banked LM CacheCORE g MD. MBIST consists of a controller Background pattern generator address generator writeread control signal and a memory with its wrapper. In terms of memory access hardware regularity and simplicity and throughput the proposed VLSI architecture is more efficient than the previously proposedKeywords.

Source: pinterest.com

Source: pinterest.com

Larger memories start to suffer excess delay along bit and word lines. In terms of memory access hardware regularity and simplicity and throughput the proposed VLSI architecture is more efficient than the previously proposedKeywords. Intels 22nm SRAM cell. Provide address to access a word of data No correlation between successive addresses Block oriented. Cell array design with row-driven source line in block shunt architecture applicable to future 6f 2 1t1mtj memory.

Source: ece-research.unm.edu

Source: ece-research.unm.edu

Sketch our vision of a VLSI architecture in 2009 in Section 4. SRAM CMOS VLSI Design 4th Ed. Lecture 8 Memory CS250 UC Berkeley Fall 2010. Advanced VLSI Design Memory CMPE 640 Memory Architecture This strategy works well for memories up to 64 Kbits to 256 Kbits. DRAM DDR Memory Architecture RTL Digital Front End DV Verification Architecture VLSI ECE.

Source: pinterest.com

Source: pinterest.com

Structured VLSI design is a modular methodology originated by Carver Mead and Lynn Conway for saving microchip area by minimizing the interconnect fabrics area. Large on-chip memories built from arrays of static RAM bitcells where each bit cell holds a bistable cross- coupled inverters and two access transistors. Provide address to access a word of data No correlation between successive addresses Block oriented. Cell array design with row-driven source line in block shunt architecture applicable to future 6f 2 1t1mtj memory. SRAM Memory Layout Design in 180nm Technology Praveen K N MTech in VLSI Design Embedded Systems JSS Academy of Technical Education Bengaluru India B.

Source: slideplayer.com

Source: slideplayer.com

A 0 A_b 1 bit 1 bit_b 0 Force A_b low then A. MBIST consists of a controller Background pattern generator address generator writeread control signal and a memory with its wrapper. The memory core consists of an array of transistors placed on a word-linebit-line grid The memory is programmed by selectively disabling or enabling some of those devices in a ROM this is accomplished by mask level in a. The goal of the project is to develop a sort algorithm to run on an mMPU which is based on emerging memory technology of ReRAM. Provide address to access a word of data No correlation between successive addresses Block oriented.

Source: vlsi.eelabs.technion.ac.il

Source: vlsi.eelabs.technion.ac.il

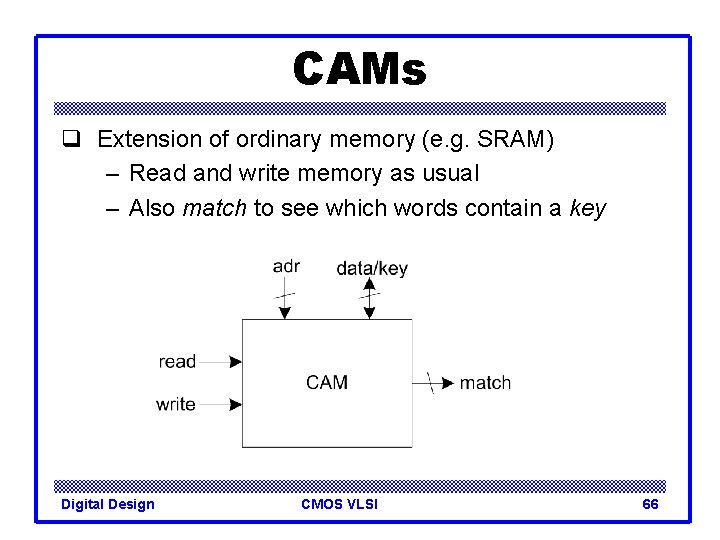

Read and write large blocks of data at a time Content-addressable. Cell array design with row-driven source line in block shunt architecture applicable to future 6f 2 1t1mtj memory. A third dimension is added. 7 SRAM Write Drive one bitline high the other low Then turn on wordline Bitlines overpower cell with new value Ex. Efficient VLSI Architecture for Memetic Vector Quantizer Design 155 The hardware architecture of the MA II and MA III can be viewed as a user logic in the NIOS-based SOPC system NIOS II Processor Reference Handbook.

Source: slideshare.net

Source: slideshare.net

Lecture 8 Memory CS250 UC Berkeley Fall 2010. The Memristive Memory Processing Unit mMPU is a new process-in-memory computer architecture which performs the computation without moving the data from the computers main memory RAM. SRAM CMOS VLSI DesignCMOS VLSI Design 4th Ed. Large on-chip memories built from arrays of static RAM bitcells where each bit cell holds a bistable cross- coupled inverters and two access transistors. The architecture of Memory built-in self-test is shown in the Figure.

Source: ece-research.unm.edu

Source: ece-research.unm.edu

DRAM DDR Memory Architecture RTL Digital Front End DV Verification Architecture VLSI ECE. Efficient VLSI Architecture for Memetic Vector Quantizer Design 155 The hardware architecture of the MA II and MA III can be viewed as a user logic in the NIOS-based SOPC system NIOS II Processor Reference Handbook. Advanced topics in system-level design issues z Description language issues C-based system description z z. 23 SRAM Memory Architecture The Architecture of SRAM memory which is asynchronous design having memory locations in random order at a fixed rate. The fundamental chal-lenges involved in building such a system.

Source: slideplayer.com

Source: slideplayer.com

Structured VLSI design is a modular methodology originated by Carver Mead and Lynn Conway for saving microchip area by minimizing the interconnect fabrics area. This is obtained by repetitive arrangement of rectangular macro blocks which can be interconnected using wiring by abutment. Cell array design with row-driven source line in block shunt architecture applicable to future 6f 2 1t1mtj memory. Read and write large blocks of data at a time Content-addressable. ¾ Architecture datapath register memory bus control logic z Operation scheduling z Resource allocation 4.

Source: slideplayer.com

Source: slideplayer.com

Provide address to access a word of data No correlation between successive addresses Block oriented. The memory core consists of an array of transistors placed on a word-linebit-line grid The memory is programmed by selectively disabling or enabling some of those devices in a ROM this is accomplished by mask level in a. Architecture of 3D DVLSI System Interconnect Wide SIMD Vector CORE GPP CORE System Many-Banked LM Cache Global Memory Wide SIMD Vector CORE GPPLevel SVP CORE Many-Banked LM CacheCORE g MD. Read and write large blocks of data at a time Content-addressable. Synthesized using the memory efficient architecture.

Source: pinterest.com

Source: pinterest.com

Read and write large blocks of data at a time Content-addressable. Sketch our vision of a VLSI architecture in 2009 in Section 4. A 0 A_b 1 bit 1 bit_b 0 Force A_b low then A. 14 Decoders n2 ndecoder consists of 2 n-input AND gates One needed for each row of memory Build AND from NAND or NOR gates Static CMOS Pseudo-nMOS. The architecture of Memory built-in self-test is shown in the Figure.

Source: ece-research.unm.edu

Source: ece-research.unm.edu

Search memory for match against partial data Serial Access. Sketch our vision of a VLSI architecture in 2009 in Section 4. A 0 A_b 1 bit 1 bit_b 0 Force A_b low then A. SRAM CMOS VLSI Design 4th Ed. SRAM CMOS VLSI DesignCMOS VLSI Design 4th Ed.

Source: design-reuse.com

Source: design-reuse.com

The system is built from 4Gb DRAM chips each of which contains 64 small but powerful processors. The architecture of Memory built-in self-test is shown in the Figure. Structured VLSI design is a modular methodology originated by Carver Mead and Lynn Conway for saving microchip area by minimizing the interconnect fabrics area. SRAM Memory Layout Design in 180nm Technology Praveen K N MTech in VLSI Design Embedded Systems JSS Academy of Technical Education Bengaluru India B. Large on-chip memories built from arrays of static RAM bitcells where each bit cell holds a bistable cross- coupled inverters and two access transistors.

This site is an open community for users to share their favorite wallpapers on the internet, all images or pictures in this website are for personal wallpaper use only, it is stricly prohibited to use this wallpaper for commercial purposes, if you are the author and find this image is shared without your permission, please kindly raise a DMCA report to Us.

If you find this site beneficial, please support us by sharing this posts to your preference social media accounts like Facebook, Instagram and so on or you can also bookmark this blog page with the title memory architecture in vlsi design by using Ctrl + D for devices a laptop with a Windows operating system or Command + D for laptops with an Apple operating system. If you use a smartphone, you can also use the drawer menu of the browser you are using. Whether it’s a Windows, Mac, iOS or Android operating system, you will still be able to bookmark this website.