Your Systolic architecture design images are available in this site. Systolic architecture design are a topic that is being searched for and liked by netizens today. You can Get the Systolic architecture design files here. Find and Download all free vectors.

If you’re looking for systolic architecture design pictures information connected with to the systolic architecture design keyword, you have pay a visit to the ideal blog. Our website always gives you hints for downloading the maximum quality video and image content, please kindly search and find more enlightening video articles and images that fit your interests.

Systolic Architecture Design. The Systolic Array 1-4 is this design in an integral part of the main processor. Systolic architectures are designed by using linear mapping techniques on regular dependence graphs DG. Systolic Architecture Design Systolic Architecture a general methodology for mapping high-level computations into hardware structures. Architectures for systolic arrays and also provides a general method for mapping an algorithm to a systolic array.

Used as a coprocessor in combination with a host computer and. In a systolic systemdataflowsfromthecomputermemcoryin a rhythmic fashion passing through many processing muchas to. However they are usually implemented to. Regular Dependence Graph. In computer architecture a systolic architecture is a array of processing elements it forms a pipelined network arrangement of processing elements called as cell. This can be rectangular triangular or.

The systolic model are allowed.

This can be rectangular triangular or. A network of PEs that rhythmically compute and pass data through the system. Not all PEs are identical small deviations are allowed especially for PEs at the border of the system. The Systolic Array 1-4 is this design in an integral part of the main processor. The systolic arrays has a regular and simple design ie They are. Regular Dependence Graph.

Source: telesens.co

Source: telesens.co

This is the reason that. A network of PEs that rhythmically compute and pass data through the system. In computer architecture a systolic architecture is a array of processing elements it forms a pipelined network arrangement of processing elements called as cell. Introduction 13 Systolic architecture systolic array A network of processing elements PEs that rhythmically compute and pass data through the system. Systolic arrays SAs are among these architectures being composed of a grid of equal processing elements that are locally interconnected.

Source: slideserve.com

Source: slideserve.com

Simple and Regular Design. Regular Dependence Graph. All the PEs in the systolic array are uniform and fully pipelined. The Systolic portion of the Processor is treated as an array of ALUs and it is controlled. DSP in VLSI Design Shao-Yi Chien 2.

Source: sciencedirect.com

Source: sciencedirect.com

Used as a coprocessor in combination with a host computer and. However they are usually implemented to. Used as a coprocessor in combination with a host computer and. The Systolic portion of the Processor is treated as an array of ALUs and it is controlled. First we design a systolic program in a very general architecture referred to as Basic Systolic Architecture and establish the correctness of the implementation.

However they are usually implemented to. Systolic architecture ageneralmethodologyformapping high-level computations into hardware structures. A network of PEs that rhythmically compute and pass data through the system. This is the reason that. 82 DATA FLOW ARCHITECTURE To demonstrate the behavior of a data flow machine a graph called a data flow.

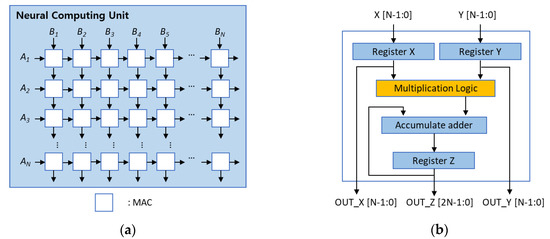

Source: mdpi.com

Source: mdpi.com

Systolic arrays SAs are among these architectures being composed of a grid of equal processing elements that are locally interconnected. Architectures for systolic arrays and also provides a general method for mapping an algorithm to a systolic array. Why Systolic Architecture It can be used for special purpose processing architecture because of 1. The design and implementatioa of high- VLSI systems. The systolic arrays has a regular and simple design ie They are.

From January to September 198t he was an architecture to ESL Itic a subsidiary or tions directly on chips and in theoretical foundations ol- VLSI Computations. Systolic architectures are designed by using linear mapping techniques on regular dependence graphs DG. Introduction 13 Systolic architecture systolic array A network of processing elements PEs that rhythmically compute and pass data through the system. In computer architecture a systolic architecture is a array of processing elements it forms a pipelined network arrangement of processing elements called as cell. Cost effective array is.

Source: sciencedirect.com

Source: sciencedirect.com

Regular Dependence Graph. Systolic architecture ageneralmethodologyformapping high-level computations into hardware structures. Systolic arrays use local instruction codes synchronized globally. This is the reason that. DSP in VLSI Design Shao-Yi Chien 2.

Source: sciencedirect.com

Source: sciencedirect.com

The systolic arrays has a regular and simple design ie They are. Systolic Architecture Design Systolic Architecture a general methodology for mapping high-level computations into hardware structures. First we design a systolic program in a very general architecture referred to as Basic Systolic Architecture and establish the correctness of the implementation. This is the reason that. DSP in VLSI Design Shao-Yi Chien 2.

Source: researchgate.net

Source: researchgate.net

This can be rectangular triangular or. Used as a coprocessor in combination with a host computer and. All the PEs in the systolic array are uniform and fully pipelined. 82 DATA FLOW ARCHITECTURE To demonstrate the behavior of a data flow machine a graph called a data flow. This is the reason that.

Source: slideserve.com

Source: slideserve.com

This is the reason that. However they are usually implemented to. The design and implementatioa of high- VLSI systems. The presence of an edge in a certain direction at any node in the DG represents presence of an edge in the same direction at all nodes in the DG. Why Systolic Architecture It can be used for special purpose processing architecture because of 1.

Source: computer.org

Source: computer.org

This is the reason that. The systolic arrays has a regular and simple design ie They are. Not all PEs are identical small deviations are allowed especially for PEs at the border of the system. Systolic Architecture Design Systolic Architecture a general methodology for mapping high-level computations into hardware structures. 82 DATA FLOW ARCHITECTURE To demonstrate the behavior of a data flow machine a graph called a data flow.

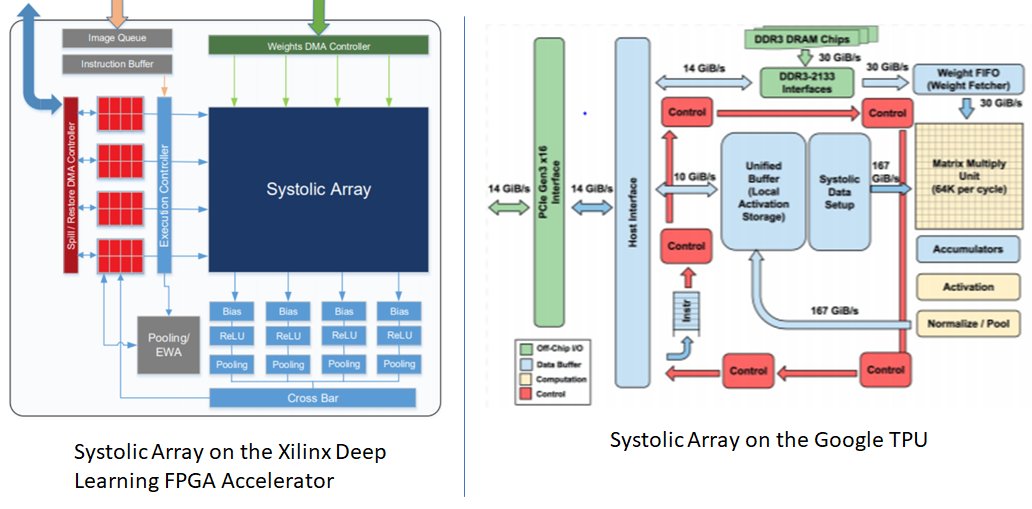

Source: cplu.medium.com

Source: cplu.medium.com

Regular Dependence Graph. A network of PEs that rhythmically compute and pass data through the system. In computer architecture a systolic architecture is a array of processing elements it forms a pipelined network arrangement of processing elements called as cell. This is the reason that. Systolic Architecture What is systolic architecture also called Systolic Arrays.

Source: design-reuse.com

Source: design-reuse.com

Used as a coprocessor in combination with a host computer and. The design and implementatioa of high- VLSI systems. From January to September 198t he was an architecture to ESL Itic a subsidiary or tions directly on chips and in theoretical foundations ol- VLSI Computations. Introduction 13 Systolic architecture systolic array A network of processing elements PEs that rhythmically compute and pass data through the system. The systolic model are allowed.

Source: computer.org

Source: computer.org

Used as a coprocessor in combination with a host computer and. The design and implementatioa of high- VLSI systems. Next we show how efficient. Not all PEs are identical small deviations are allowed especially for PEs at the border of the system. Systolic architectures are designed by using linear mapping techniques on regular dependence graphs DG.

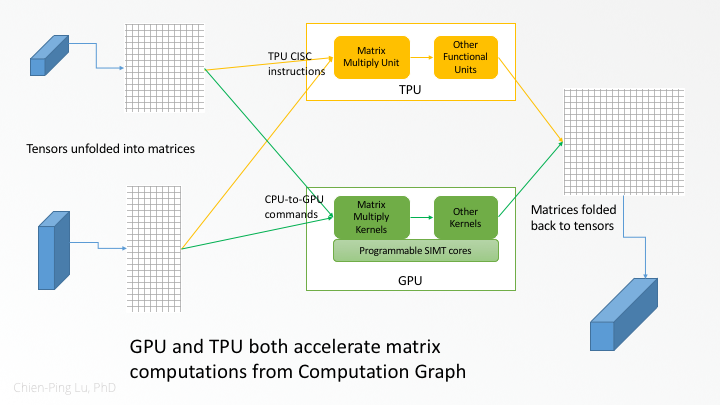

Source: cplu.medium.com

Source: cplu.medium.com

It is a specialized form of parallel. Systolic architectures are designed by using linear mapping techniques on regular dependence graphs DG. In computer architecture a systolic architecture is a pipelined network arrangement of Processing Elements PEs called cells. Regular Dependence Graph. First we design a systolic program in a very general architecture referred to as Basic Systolic Architecture and establish the correctness of the implementation.

Source: sciencedirect.com

Source: sciencedirect.com

Systolic architectures are designed by using linear mapping techniques on regular dependence graphs DG. Systolic Architecture Design Systolic Architecture a general methodology for mapping high-level computations into hardware structures. Introduction 13 Systolic architecture systolic array A network of processing elements PEs that rhythmically compute and pass data through the system. Regular Dependence Graph. Systolic architectures are designed by using linear mapping techniques on regular dependence graphs DG.

Source: cplu.medium.com

Source: cplu.medium.com

The presence of an edge in. The systolic arrays has a regular and simple design ie They are. This can be rectangular triangular or. Systolic architectures are designed by using linear mapping techniques on regular dependence graphs DG. Not all PEs are identical small deviations are allowed especially for PEs at the border of the system.

Source: sciencedirect.com

Source: sciencedirect.com

Why Systolic Architecture It can be used for special purpose processing architecture because of 1. This is the reason that. Introduction 13 Systolic architecture systolic array A network of processing elements PEs that rhythmically compute and pass data through the system. DSP in VLSI Design Shao-Yi Chien 2. A network of PEs that rhythmically compute and pass data through the system.

This site is an open community for users to do submittion their favorite wallpapers on the internet, all images or pictures in this website are for personal wallpaper use only, it is stricly prohibited to use this wallpaper for commercial purposes, if you are the author and find this image is shared without your permission, please kindly raise a DMCA report to Us.

If you find this site good, please support us by sharing this posts to your preference social media accounts like Facebook, Instagram and so on or you can also save this blog page with the title systolic architecture design by using Ctrl + D for devices a laptop with a Windows operating system or Command + D for laptops with an Apple operating system. If you use a smartphone, you can also use the drawer menu of the browser you are using. Whether it’s a Windows, Mac, iOS or Android operating system, you will still be able to bookmark this website.